Flip - Flops 2m6m26

This document was ed by and they confirmed that they have the permission to share it. If you are author or own the copyright of this book, please report to us by using this report form. Report 3i3n4

Overview 26281t

& View Flip - Flops as PDF for free.

More details 6y5l6z

- Words: 1,174

- Pages: 12

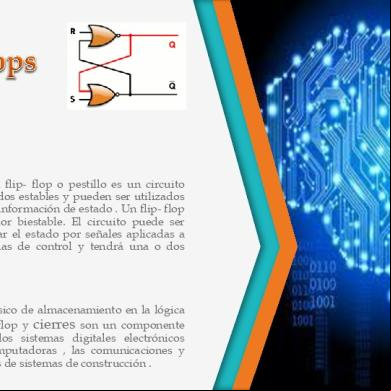

En electrónica, un flip- flop o pestillo es un circuito que tiene dos estados estables y pueden ser utilizados para almacenar la información de estado . Un flip- flop es un multivibrador biestable. El circuito puede ser hecho para cambiar el estado por señales aplicadas a una o más entradas de control y tendrá una o dos salidas .

Es el elemento básico de almacenamiento en la lógica secuencial . Flip- flop y cierres son un componente fundamental de los sistemas digitales electrónicos usados en las computadoras , las comunicaciones y muchos otros tipos de sistemas de construcción .

Aplicación De un Flip-Flop • Flip- flops y pestillos se utilizan como elementos de almacenamiento de datos. Tal almacenamiento de datos se puede utilizar para el almacenamiento de estado , y un circuito de este tipo se describe como la lógica secuencial . Cuando se utiliza en una máquina de estado finito , la salida y el siguiente estado dependen no sólo de su entrada de corriente , sino también de su estado actual ( y por lo tanto , las entradas anteriores ) . También se puede utilizar para el recuento de impulsos , y para la sincronización de señales de entrada variable - cronometrados a alguna señal de temporización de referencia .

Flip- Flops (R-S NOR) construido a partir de un par de acoplamiento cruzado las puertas NOR Rojo y negro significan '1 'lógico y '0', respectivamente. Al utilizar puertas estáticas como bloques de construcción, el pestillo más fundamental es el latch SR simple, donde destacan S y R para el grupo y se restauran. Puede ser construido a partir de un par de puertas de acoplamiento cruzado logica NOR. El bit almacenado está presente en la salida marcada P.

Mientras que las entradas S y R son bajos, la retroalimentación mantiene las salidas Q y Q en un estado constante, con el complemento de Q Q. Si S (Set) es pulsada de alto, mientras que R (Reset) se mantiene baja, la salida Q se ve obligado de altura, y se mantiene alta cuando S devuelve a menor, de manera similar, si se pulsa en I, mientras que S se mantiene baja, la salida Q se fuerza bajo, y se mantiene baja cuando R vuelve a menor.

Flip- Flops (R-S NAND) Es un modelo alternativo del latch SR sencillo que se construye con puertas lógicas NAND. Establecer y restablecer las señales ahora convertido en activos bajos, S denota y R, respectivamente. De lo contrario, la operación es idéntica a la de la latch SR. Históricamente, SR-cierres han sido predominantes a pesar del inconveniente de notación de las entradas activas bajas.

Flip- Flops (J-K) aumenta el comportamiento del flip-flop SR (J = Set, K = Restablecer) interpretando el S = R = 1 condición de "flip" o el comando cambiar. Específicamente, la combinación J = 1, K = 0 es un comando para establecer el flip-flop; la combinación J = 0, K = 1 es un comando para restablecer el flip-flop, y la combinación J = K = 1 es un comando para alternar el flip-flop, es decir, cambie su salida al complemento lógico de su valor actual. Ajuste J = K = 0 no se traduce en un flip-flop, sino más bien, mantendrá el estado actual. Por lo tanto, para sintetizar un flip-flop D, basta con establecer K igual al complemento de J. Del mismo modo, para sintetizar un flip-flop T, ajuste K igual a J. El flip-flop JK es un flip-flop universales, ya que puede ser configurado para trabajar como un flip-flop SR, un flip-flop, o un T flip-flop.

y la tabla de verdad correspondiente es:

es ampliamente utilizado. También se conoce como "date" o "delay" flip-flop. El flip-flop D captura el valor de la entrada D en una porción definida del ciclo de reloj (tal como el borde de subida del reloj). Ese valor capturado se convierte en la salida Q. En otras ocasiones, la salida Q no cambia. El flipflop puede ser visto como una célula de memoria, un mantenedor de orden cero, o una línea de retardo. Tabla de Verdad:

('X' indica una condición que no importa, lo que significa que la señal es irrelevante)

Flip- Flops (D)

La mayoría de los de tipo D flip-flops en circuitos integrados tienen la capacidad de ser forzado al establecer o restablecer el estado (que no tiene en cuenta las entradas D y el reloj), al igual que un flip-flop SR. Por lo general, el S = R = 1 condición ilegal se resuelve en D-tipo flip-flops. Al establecer S = R = 0, el flip-flop se puede utilizar como se describe anteriormente. Esta es la tabla de verdad para los otros S y configuraciones R sea posible:

Flip- Flops (D)

Flip- Flops (T) Si la entrada T es alta, el flip-flop T cambia de estado ("alterna") cada vez que se estroboscópicamente la entrada de reloj. Si la entrada T está baja, el flip-flop mantiene el valor anterior. Este comportamiento se describe por la ecuación característica:

Cuando se lleva a cabo T alta, el conmutador biestable divide la frecuencia de reloj por dos, es decir, si la frecuencia de reloj es 4 MHz, la frecuencia de salida obtenida desde el flip-flop será de 2 MHz. Esta "división por" característica tiene aplicación en diversos tipos de contadores digitales

Flip- Flops (Máster- Slave) se crea mediante la conexión de dos pestillos gatead D en serie , y la inversión de la entrada de habilitación a uno de ellos . Se llama maestro-esclavo porque el segundo pestillo en la serie sólo cambia en respuesta a un cambio en la primera ( principal ) el pestillo .

Un maestro-esclavo D flip- flop. Responde en el flanco descendente de la entrada de habilitación ( por lo general un reloj )

Flip- Flops (Máster- Slave) Como la señal de reloj pasa a nivel alto ( 0 a 1 ) la invertida " enable" del primer pestillo pasa a nivel bajo ( 1 a 0 ) y el valor visto en la entrada al pestillo principal está " bloqueado " . Casi simultáneamente, el doble invertido " activar" de la segunda o "esclavo" transiciones pestillo D de bajo a alto ( 0-1 ) con la señal de reloj . Esto permite que la señal capturada en el borde ascendente del reloj por el ahora "bloqueado" cerrojo maestro pase a través de la traba "esclavo " . Cuando la señal de reloj regresa a baja ( 1 a 0) , la salida del pestillo "esclavo " está "bloqueada " , y el valor visto en el último flanco de subida del reloj se lleva a cabo mientras el pestillo "maestro" comienza a aceptar la nueva valores en preparación para el siguiente flanco de reloj ascendente .

Al eliminar el inversor más a la izquierda en el circuito al lado , un flip -flop de tipo D que destella en el flanco de bajada de una señal de reloj puede ser obtenida. Esto tiene una tabla de verdad de esta manera:

Es el elemento básico de almacenamiento en la lógica secuencial . Flip- flop y cierres son un componente fundamental de los sistemas digitales electrónicos usados en las computadoras , las comunicaciones y muchos otros tipos de sistemas de construcción .

Aplicación De un Flip-Flop • Flip- flops y pestillos se utilizan como elementos de almacenamiento de datos. Tal almacenamiento de datos se puede utilizar para el almacenamiento de estado , y un circuito de este tipo se describe como la lógica secuencial . Cuando se utiliza en una máquina de estado finito , la salida y el siguiente estado dependen no sólo de su entrada de corriente , sino también de su estado actual ( y por lo tanto , las entradas anteriores ) . También se puede utilizar para el recuento de impulsos , y para la sincronización de señales de entrada variable - cronometrados a alguna señal de temporización de referencia .

Flip- Flops (R-S NOR) construido a partir de un par de acoplamiento cruzado las puertas NOR Rojo y negro significan '1 'lógico y '0', respectivamente. Al utilizar puertas estáticas como bloques de construcción, el pestillo más fundamental es el latch SR simple, donde destacan S y R para el grupo y se restauran. Puede ser construido a partir de un par de puertas de acoplamiento cruzado logica NOR. El bit almacenado está presente en la salida marcada P.

Mientras que las entradas S y R son bajos, la retroalimentación mantiene las salidas Q y Q en un estado constante, con el complemento de Q Q. Si S (Set) es pulsada de alto, mientras que R (Reset) se mantiene baja, la salida Q se ve obligado de altura, y se mantiene alta cuando S devuelve a menor, de manera similar, si se pulsa en I, mientras que S se mantiene baja, la salida Q se fuerza bajo, y se mantiene baja cuando R vuelve a menor.

Flip- Flops (R-S NAND) Es un modelo alternativo del latch SR sencillo que se construye con puertas lógicas NAND. Establecer y restablecer las señales ahora convertido en activos bajos, S denota y R, respectivamente. De lo contrario, la operación es idéntica a la de la latch SR. Históricamente, SR-cierres han sido predominantes a pesar del inconveniente de notación de las entradas activas bajas.

Flip- Flops (J-K) aumenta el comportamiento del flip-flop SR (J = Set, K = Restablecer) interpretando el S = R = 1 condición de "flip" o el comando cambiar. Específicamente, la combinación J = 1, K = 0 es un comando para establecer el flip-flop; la combinación J = 0, K = 1 es un comando para restablecer el flip-flop, y la combinación J = K = 1 es un comando para alternar el flip-flop, es decir, cambie su salida al complemento lógico de su valor actual. Ajuste J = K = 0 no se traduce en un flip-flop, sino más bien, mantendrá el estado actual. Por lo tanto, para sintetizar un flip-flop D, basta con establecer K igual al complemento de J. Del mismo modo, para sintetizar un flip-flop T, ajuste K igual a J. El flip-flop JK es un flip-flop universales, ya que puede ser configurado para trabajar como un flip-flop SR, un flip-flop, o un T flip-flop.

y la tabla de verdad correspondiente es:

es ampliamente utilizado. También se conoce como "date" o "delay" flip-flop. El flip-flop D captura el valor de la entrada D en una porción definida del ciclo de reloj (tal como el borde de subida del reloj). Ese valor capturado se convierte en la salida Q. En otras ocasiones, la salida Q no cambia. El flipflop puede ser visto como una célula de memoria, un mantenedor de orden cero, o una línea de retardo. Tabla de Verdad:

('X' indica una condición que no importa, lo que significa que la señal es irrelevante)

Flip- Flops (D)

La mayoría de los de tipo D flip-flops en circuitos integrados tienen la capacidad de ser forzado al establecer o restablecer el estado (que no tiene en cuenta las entradas D y el reloj), al igual que un flip-flop SR. Por lo general, el S = R = 1 condición ilegal se resuelve en D-tipo flip-flops. Al establecer S = R = 0, el flip-flop se puede utilizar como se describe anteriormente. Esta es la tabla de verdad para los otros S y configuraciones R sea posible:

Flip- Flops (D)

Flip- Flops (T) Si la entrada T es alta, el flip-flop T cambia de estado ("alterna") cada vez que se estroboscópicamente la entrada de reloj. Si la entrada T está baja, el flip-flop mantiene el valor anterior. Este comportamiento se describe por la ecuación característica:

Cuando se lleva a cabo T alta, el conmutador biestable divide la frecuencia de reloj por dos, es decir, si la frecuencia de reloj es 4 MHz, la frecuencia de salida obtenida desde el flip-flop será de 2 MHz. Esta "división por" característica tiene aplicación en diversos tipos de contadores digitales

Flip- Flops (Máster- Slave) se crea mediante la conexión de dos pestillos gatead D en serie , y la inversión de la entrada de habilitación a uno de ellos . Se llama maestro-esclavo porque el segundo pestillo en la serie sólo cambia en respuesta a un cambio en la primera ( principal ) el pestillo .

Un maestro-esclavo D flip- flop. Responde en el flanco descendente de la entrada de habilitación ( por lo general un reloj )

Flip- Flops (Máster- Slave) Como la señal de reloj pasa a nivel alto ( 0 a 1 ) la invertida " enable" del primer pestillo pasa a nivel bajo ( 1 a 0 ) y el valor visto en la entrada al pestillo principal está " bloqueado " . Casi simultáneamente, el doble invertido " activar" de la segunda o "esclavo" transiciones pestillo D de bajo a alto ( 0-1 ) con la señal de reloj . Esto permite que la señal capturada en el borde ascendente del reloj por el ahora "bloqueado" cerrojo maestro pase a través de la traba "esclavo " . Cuando la señal de reloj regresa a baja ( 1 a 0) , la salida del pestillo "esclavo " está "bloqueada " , y el valor visto en el último flanco de subida del reloj se lleva a cabo mientras el pestillo "maestro" comienza a aceptar la nueva valores en preparación para el siguiente flanco de reloj ascendente .

Al eliminar el inversor más a la izquierda en el circuito al lado , un flip -flop de tipo D que destella en el flanco de bajada de una señal de reloj puede ser obtenida. Esto tiene una tabla de verdad de esta manera: